Intel 8086 — первый 16-битный микропроцессор компании Intel. Разрабатывался с весны 1976 года и выпущен 8 июня 1978 года. Реализованная в процессоре архитектура набора команд стала основой широко известной архитектуры x86. Процессоры этой архитектуры стали наиболее успешной линией процессоров Intel. Современные процессоры этой архитектуры сохраняют возможность выполнять все команды этого набора.

x86 — архитектура процессора и одноимённый набор команд, впервые реализованные в процессорах компании Intel.

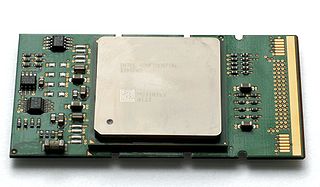

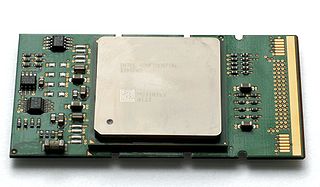

Intel 80486 — 32-битный скалярный x86-совместимый микропроцессор четвёртого поколения, построенный на гибридном CISC-RISC-ядре и выпущенный фирмой Intel 10 апреля 1989 года. Этот микропроцессор является усовершенствованной версией микропроцессора 80386. Впервые он был продемонстрирован на выставке Comdex Fall, осенью 1989 года. Это был первый микропроцессор со встроенным математическим сопроцессором (FPU). Применялся преимущественно в настольных ПК, в высокопроизводительных рабочих станциях, в серверах и портативных ПК.

Центра́льный проце́ссор — электронный блок либо интегральная схема, исполняющая машинные инструкции, главная часть аппаратного обеспечения компьютера или программируемого логического контроллера. Иногда этот компонент называют просто процессором.

VLIW — архитектура процессоров с несколькими вычислительными устройствами. Характеризуется тем, что одна инструкция процессора содержит несколько операций, которые должны выполняться параллельно. Фактически это «видимое программисту» микропрограммное управление, когда машинный код представляет собой лишь немного свёрнутый микрокод для непосредственного управления аппаратурой.

x86-64 — 64-битная версия архитектуры x86, разработанная компанией AMD и представленная в 2000 году, позволяющая выполнять программы в 64-разрядном режиме.

Intel Core — торговая марка микропроцессоров, производимых компанией Intel. Процессоры Core являются преемниками процессоров предыдущего поколения, представленных моделями Pentium и Celeron. Для серверов имеются более «продвинутые» версии процессоров Core под маркой Xeon. В данный момент серия насчитывает 13 поколений.

MMX — коммерческое название дополнительного SIMD-набора инструкций, разработанного компанией Intel и впервые представленного в 1997 году одновременно с линией процессоров Pentium MMX. Набор инструкций был предназначен для ускорения процессов кодирования/декодирования потоковых аудио- и видеоданных. Является развитием технологий, предложенных в микропроцессоре i860. Разработан в лаборатории Intel в Хайфе, Израиль, в первой половине 1990-х.

Core 2 Duo — семейство 64-разрядных микропроцессоров, предназначенных для клиентских систем и основанных на микроархитектуре Core, разработанных и производимых корпорацией Intel.

Core 2 — восьмое поколение микропроцессоров архитектуры x86-64 корпорации Intel, основанное на микроархитектуре Core. Это потомок микроархитектуры Intel P6, на которой, начиная с процессора Pentium Pro, построено большинство микропроцессоров Intel, исключая процессоры с архитектурой NetBurst. Введя новый бренд, от названий Pentium и Celeron Intel не отказалась, в 2007 году переведя их также на микроархитектуру Core, были доступны процессоры Pentium Dual-Core и Core Celeron. Тогда воссоединились мобильные и настольные серии продуктов.

Intel Pentium Dual-Core — микропроцессоры архитектуры x86 от Intel с 2006 по 2009 год. Процессоры основаны на 32-разрядном ядре Yonah или 64-разрядном Merom-2M, Allendale, Wolfdale-3M, Penryn-3M и Penryn-L ядре, предназначенные для мобильных или настольных ПК.

Многоя́дерный проце́ссор — центральный процессор, содержащий два и более вычислительных ядра на одном процессорном кристалле или в одном корпусе.

Intel Atom — линейка микропроцессоров архитектур x86 и x86-64, отличающихся низким энергопотреблением. Выпускаются компанией Intel. Изготавливаются по 45-нм КМОП-технологии, с конца 2011 года - по 32-нм техпроцессу, с 2013 - по 22-нм технологии, с 2014 - по 14-нм технологии. C 2022 по 10-нм технологии

Аппаратная платформа компьютера — уровень, образованный программной архитектурой компьютера на аппаратной базе.

Микроархитектура Intel Core является многоядерной микропроцессорной архитектурой, представленной фирмой Intel в 1-м квартале 2006 года. Микроархитектура Intel Core основана на обновлённой версии ядра Yonah и может рассматриваться в качестве последней итерации микроархитектуры Intel P6, которая ведёт свою историю с Pentium Pro, представленного в 1995 году. Чрезмерно высокое энергопотребление и завышенные требования к охлаждению процессоров, основанных на микроархитектуре NetBurst, и, в результате, неспособность эффективно увеличивать тактовую частоту, а также другие узкие места, такие, как неэффективность конвейера, являются главными причинами, почему Intel отказалась от микроархитектуры NetBurst. Микроархитектура Intel Core была разработана командой Intel Israel, которая ранее разработала мобильный процессор Pentium M.

Intel Core i3 — семейство процессоров x86-64 фирмы Intel.

Микроархитектура — способ, которым данная архитектура набора команд реализована в процессоре.

64 бита в информатике и вычислительной технике используется для обозначения структур и типов данных, размер которых в памяти компьютеров составляет 64 бита, что равно 8 8-битовым байтам. Архитектуры компьютеров, которые широко используют регистры, адресные шины или шины данных, разрядности 64 бита, называются 64-битными архитектурами.

Intel Architecture — система архитектур процессора, разрабатываемых компанией Intel. Данные архитектуры были совместимы только со своим набором инструкций и одна из них использовалась в процессорах других компаний. В настоящее время подразделяется на две архитектуры: IA-32 и IA-64.