Параллелизм на уровне команд

Параллелизм на уровне команд (англ. Instruction-level parallelism — ILP) является мерой того, какое множество операций в компьютерной программе может выполняться одновременно. Потенциальное совмещение выполнения команд называется «параллелизмом на уровне команд».

Описание

Есть два подхода к выявлению параллелизма (parallelism extraction) на уровне команд:

- аппаратные средства — выявлением параллелизма в потоке операций занимаются специальные схемы процессора при исполнении кода программ;

- программное обеспечение — выявлением параллелизма занимается компилятор, который формирует исполняемый код программы под специальный процессор.

Уровень аппаратного обеспечения осуществляет динамический параллелизм, тогда как уровень программного обеспечения реализует статический параллелизм. Современные высокопроизводительные процессоры x86 (AMD Ryzen, Intel Core) работают на динамической последовательности параллельного выполнения (Внеочередное исполнение команд). Статический параллелизм применялся в процессорах Itanium (однако в Itanium 2 применялся гибридный подход).

Рассмотрим следующую программу:

- e = a + b

- f = c + d

- m = e * f

Операция 3 зависит от результатов операций 1 и 2, поэтому она не может быть вычислена, пока не будут завершены 1 и 2. Однако операции 1 и 2 не зависят от других операций, поэтому они могут быть вычислены одновременно. Если предположить, что каждая операция может быть завершена за одну единицу времени, то эти три инструкции могут быть завершены в общей сложности за две единицы времени, обеспечивая параллелизм равный 3/2.

Цель разработчиков компилятора и процессора заключается в выявлении параллелизма и получении от него максимального выигрыша. Обычные программы, как правило, написаны под последовательную модель исполнения, где команды выполняются одна за другой в порядке, установленном программистом. ILP позволяет компилятору и/или процессору распараллеливать выполнение нескольких инструкций или даже изменять порядок их выполнения.

Сколько ILP присутствует в программе сильно зависит от области её применения. В некоторых областях, таких как компьютерная графика и научные вычисления, число может быть очень большим. Тем не менее такие задачи как криптография могут демонстрировать гораздо меньше параллелизма.

Аппаратные методы выявления и использования параллелизма:

- Вычислительный конвейер, где выполнение нескольких инструкций может частично перекрываться;

- Суперскалярное выполнение операций, в которой несколько функциональных блоков используется для выполнения нескольких команд одновременно;

- Внеочередное исполнение, где инструкции выполняются в любом порядке, который не нарушает зависимости данных. Обратите внимание, что этот метод не зависит ни от конвейера, ни от суперскалярного выполнения. Текущие реализации внеочередного исполнения динамически (то есть во время выполнения программы и без помощи со стороны компилятора) получают ILP из обычных программ. Альтернативой является получение параллелизма во время компиляции и передача этой информации аппаратному обеспечению. Из-за сложности масштабирования техники внеочередного исполнения отрасль пересмотрела набор команд, которые явно кодируют несколько независимых операций в инструкции;

- Переименование регистров — метод, используемый для устранения ненужной сериализации (последовательного выполнения) операций, к которой приводит переиспользование регистров этими операциями, и используемый для внеочередного исполнения;

- Спекулятивное исполнение, которое позволяет выполнять инструкции целиком или частично до того, как станет ясно, нужно ли это выполнение. Часто используемой формой спекулятивного исполнения является спекулятивное исполнение потока управления, при котором инструкции (например, переход) за потоком управления выполняются до того, как определится та ветка программы, которую определяет инструкция перехода. Были предложены и используются несколько других форм спекулятивного исполнения, в том числе для спекулятивного исполнения, обусловленного предсказанием значения, предсказание зависимости по памяти и предсказание задержек кэша;

- Предсказание переходов, которое используется, чтобы избежать простаивания для разрешения управления зависимостями. Предсказатель переходов используется со спекулятивным исполнением.

Потоковые архитектуры представляют собой другой класс архитектур, где ILP явно указаны, см., например, архитектуру TRIPS.

Реализации

Ранние реализации ILP в таких мейнфреймах, как IBM System/360 Model 91, использовали методы ILP, чтобы преодолеть ограничения, налагаемые относительно небольшим регистровым файлом.

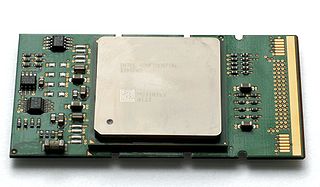

В микропроцессорах различные формы параллелизма на уровне инструкций стали применяться с конца 1980-х. В качестве примера первых суперскалярных процессоров можно привести Intel 960CA (1989 год[1]), IBM Power RS/6000 (1990 год), DEC Alpha 21064 (1992 год)[2]. Внеочередное исполнение команд и переименование регистров в микропроцессорах впервые было реализовано в IBM POWER1 (1990 г.).

Первым IA-32-процессором с конвейером стал Intel 80486 (1989 г.); первым суперскалярным IA-32-процессором стал Intel Pentium (1993 г); первый IA-32-процессор с внеочередным исполнением команд и переименованием регистров — Intel Pentium Pro (1995 г.),

В период с 1999 по 2005 год компании AMD и Intel вели активную конкурентную борьбу по выпуску все более и более производительных микропроцессоров для массового потребительского и серверного рынков. В процессорах, выпущенных за этот период, обеими компаниями активно совершенствовались техники эксплуатации параллелизма на уровне команд. Уменьшение техпроцесса позволяло поместить ещё больше транзисторов на подложке процессора с целью использовать их для построения ещё более сложных и эффективных суперскалярных конвейеров.

Обе компании повышали тактовую частоту процессоров (т. н. «гонка гигагерцев»). Например, в архитектуре NetBurst компания Intel наращивала стадии вычислительного конвейера, доведя их число в Pentium 4 Prescott до 31, что позволило добиться максимальных частот, но для обычного кода (не оптимизированного специально для Pentium 4) снизило IPC[англ.] на столько, что эти процессоры проигрывали в производительности процессорам Athlon 64 с существенно меньшей тактовой частотой.

К концу 2005 года стало ясно, что все эти способы и методы начали себя исчерпывать. Закон масштабирования Деннарда перестал работать. При неизменных темпах увеличения количества транзисторов производительность самих процессоров повышалась незначительно, но при этом росло энергопотребление процессоров и их тепловыделение, приблизившись к ограничениям недорогих систем теплоотвода (power ceiling, power wall[3][4]).

С конца 2005 года рост тактовых частот и однопоточной производительности значительно замедлились[5][6][7] и отрасль производства микропроцессоров начала движение в сторону использования других уровней параллелизма, а именно параллелизма на уровне потоков и задач, реализованого в многопроцессорности, многоядерности и аппаратной многопоточности[8]. Это отразилось в свою очередь на подходах к программированию[9].

См. также

Примечания

- ↑ Ron Copeland. Intel Ready to Announce i960CA Microprocessor With 66 MIPS // InfoWorld. — 1989. — Т. 11, № 36. — С. 19. (англ.)

- ↑ Kai Hwang, Naresh Jotwani. Advanced Computer Architecture. — second edition. — McGraw-Hill Education, 2011. — С. 152. — 723 с. — ISBN 978-0-07-070210-3. (англ.)

- ↑ Christopher Mims. Why CPUs Aren't Getting Any Faster (англ.). MIT Technology review (12 октября 2010). — «power wall (the chip’s overall temperature and power consumption). .. arguably the defining limit of the power of the modern CPU.» Дата обращения: 3 сентября 2016. Архивировано 16 сентября 2016 года.

- ↑ Russell Fish. Future of computers - Part 2: The Power Wall (англ.). EDN (6 января 2012). Дата обращения: 3 сентября 2016. Архивировано 6 сентября 2016 года.

- ↑ DATA PROCESSING IN EXASCALE-CLASS COMPUTER SYSTEMS, Chuck Moore (AMD), The Salishan Conference on High Speed Computing (LANL / LLNL / SNL) April 27, 2011

- ↑ The death of CPU scaling: From one core to many — and why we’re still stuck Архивная копия от 7 сентября 2016 на Wayback Machine, Joel Hruska on February 1, 2012

- ↑ A Look Back at Single-Threaded CPU Performance Архивная копия от 14 сентября 2016 на Wayback Machine, 2012 — после 2004 г рост однопоточной производительности по SpecInt составляет около 15-20 % в год, вместо 50 % в предыдущие десять лет

- ↑ [1] Архивная копия от 7 февраля 2018 на Wayback Machine Intel Developer Forum in 2005 — Intel President Paul Otellini — «We are dedicating all of our future product development to multicore designs. We believe this is a key inflection point for the industry».

- ↑ Herb Sutter. The Free Lunch Is Over: A Fundamental Turn Toward Concurrency in Software Архивная копия от 10 июля 2016 на Wayback Machine

Литература

- David A. Patterson, John L. Hennessy. Computer Architecture: A Quantitative Approach, 5th Edition. — Morgan Kaufmann, 2011. — 856 p. — ISBN 012383872X. (англ.) — Глава 3, стр.148-247

- под ред. David Padua. Encyclopedia of Parallel Computing. — Springer, 2012. — 2366 p. — ISBN 0387098445. (англ.) — стр.935

- David Harris, Sarah Harris. Digital Design and Computer Architecture, 2nd Ed. — Morgan Kaufmann, 2012. — 712 p. — ISBN 0123944244. (англ.) — стр.444-452

- David A. Patterson, John L. Hennessy. Computer Organization and Design: The Hardware/Software Interface, 5th Edition. — Morgan Kaufmann, 2013. — 800 p. — ISBN 0124077269. (англ.) — Глава 4.10, стр.332-344