Регистр процессора

Реги́стр проце́ссора — поле заданной длины во внутрипроцессорной сверхбыстрой оперативной памяти (СОЗУ). Используется самим процессором, может быть как доступным, так и не доступным программно. Например, при выборке из памяти очередной команды она помещается в регистр команд, обращение к которому программист прописать не может.

Программно недоступные регистры

Программно недоступные регистры — любые процессорные регистры, к которым невозможно так или иначе обратиться из выполняемой программы. Пример таких регистров — уже упомянутый регистр команд.

Программно доступные регистры

Программно доступные регистры есть те, к которым возможно так или иначе обратиться из выполняемой программы. Практически каждый такой регистр обозначается своим именем-идентификатором на уровне языка ассемблера и соответствующим числовым кодом-идентификатором на уровне машинного языка. По уровню доступности программно доступные регистры неодинаковы и практически делятся на две большие подгруппы:

- системные регистры — любые регистры, программно доступные только системным программам (например, ядру операционной системы), имеющим достаточный для этого уровень системных привилегий/прав. В терминах многих машинных систем такой уровень привилегий часто называется «уровнем/режимом ядра» или «режимом супервизора». Для всех прочих программ — работающих в «режиме пользователя» — эти регистры недоступны. Примеры таких регистров: управляющие регистры и теневые регистры дескрипторов сегментов.

- регистры общего назначения (РОН) — регистры, доступные любым программам. В частности, регистры, используемые без ограничения в арифметических и логических операциях, но имеющие определённые аппаратные ограничения (например, в строковых РОН). Эти регистры не характерны для эпохи мейнфреймов типа IBM/370[1] и стали популярными в микропроцессорах архитектуры X86 — Intel 8085, Intel 8086 и последующих[2].

Специальные регистры[3] содержат данные, необходимые для работы процессора — смещения базовых таблиц, уровни доступа и т. д.

Часть специальных регистров принадлежит устройству управления, которое управляет процессором путём генерации последовательности микрокоманд.

Доступ к значениям, хранящимся в регистрах, осуществляется непосредственно на тактовой частоте процессора и, как правило, в несколько раз быстрее, чем доступ к полям в оперативной памяти (даже если кеш-память содержит нужные данные), но объём оперативной памяти намного превосходит суммарный объём процессорных регистров, суммарная «ёмкость» регистров общего назначения/данных для x86-процессоров (например, Intel 80386 и более новых) 8 регистров по 4 байта = 32 байта (В x86-64-процессорах — 16 по 8 байт = 128 байт и некоторое количество векторных регистров).

Некоторые примеры

В таблице показано количество регистров общего назначения в нескольких распространённых архитектурах микропроцессоров. Стоит отметить, что в некоторых архитектурах использование отдельных регистров может быть осложнено. Так, в SPARC и MIPS регистр номер 0 не сохраняет информацию и всегда считывается как 0, а в процессорах x86 с регистром ESP (указатель на стек) могут работать лишь некоторые команды.

| Архитектура | Целочисленных регистров | FP- регистров | Примечания |

|---|---|---|---|

| x86-32 | 8 | 8 | |

| x86-64 | 16 | 16 | |

| IBM System/360 | 16 | 4 | |

| z/Architecture | 16 | 16 | |

| Itanium | 128 | 128 | |

| SPARC | 31 | 32 | Регистр 0 (глобальный) всегда занулён |

| IBM Cell | 4~16 | 1~4 | |

| IBM POWER | 32 | 32 | |

| Power Architecture | 32 | 32 | |

| Alpha | 32 | 32 | |

| 6502 | 3 | 0 | |

| W65C816S | 5 | 0 | |

| PIC | 1 | 0 | |

| AVR | 32 | 0 | |

| ARM 32-bit[4] | 16 | различное | |

| ARM 64-bit[5] | 31 | 32 | |

| MIPS | 31 | 32 | Регистр 0 всегда занулён |

| RISC-V | 31 | 32 | Дополнительно есть регистр 0, который всегда возвращает ноль |

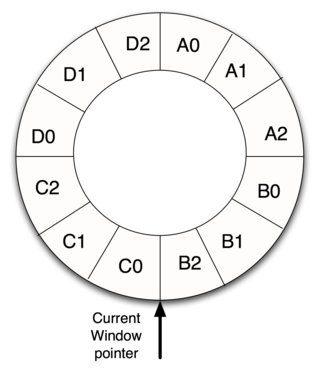

| Эльбрус 2000 | 256 | совмещены с целочисленными | 32 двухразрядных регистра, 256 = 32 глобальных регистра + 224 регистра стека процедур[6] |

Примечания

- ↑ Barbara J. Burian. Программирование на языке ассемблера системы IBM/370 упрощённый подход = A simple approach to S/370 assembly language programming. — New York: Prentice-Hall, Inc, 1977.

- ↑ Погорелый С. Д., Слободянюк Т. Ф. Программное обеспечение микропроцессорных систем. Справочник. — 2-е, переработанное и дополненное. — Киев: Тэхника, 1989. — С. 7, 48-51. — 301 с. — (Справочник специалиста). — 50 000 экз. — ISBN 5-335-00169-0.

- ↑ Intel 64 and IA-32 Architectures Software Developer’s Manual. Volume 1: Basic Architecture. 3.4 BASIC PROGRAM EXECUTION REGISTERS Архивная копия от 24 мая 2011 на Wayback Machine (англ.)

- ↑ Procedure Call Standard for the ARM Architecture. ARM Holdings (16 октября 2009). Дата обращения: 24 апреля 2012. Архивировано 28 апреля 2013 года.

- ↑ Procedure Call Standard for the ARM 64-bit Architecture. ARM Holdings (25 ноября 2011). Дата обращения: 24 апреля 2012. Архивировано 28 апреля 2013 года.

- ↑ МЦСТ. Введение в архитектуру «Эльбрус» (рус.). Альт Линукс (31 мая 2020). Дата обращения: 16 июля 2020. Архивировано 2 июня 2020 года.