Центра́льный проце́ссор — электронный блок либо интегральная схема, исполняющая машинные инструкции, главная часть аппаратного обеспечения компьютера или программируемого логического контроллера. Иногда этот компонент называют просто процессором.

RISC — архитектурный подход к проектированию процессоров, в которой быстродействие увеличивается за счёт такого кодирования инструкций, чтобы их декодирование было более простым, а время выполнения — меньшим. В системах команд первых RISC-процессоров даже отсутствовали команды умножения и деления. Это также облегчает повышение тактовой частоты и делает более эффективной суперскалярность.

CISC — тип процессорной архитектуры, которая характеризуется следующим набором свойств:

- нефиксированное значение длины команды;

- арифметические действия кодируются в одной команде;

- небольшое число регистров, каждый из которых выполняет строго определённую функцию.

Цифровой сигнальный процессор (англ. digital signal processor, DSP, цифровой процессор обработки сигналов — специализированный микропроцессор, предназначенный для обработки оцифрованных сигналов.

Арифме́тико-логи́ческое устро́йство — блок процессора, который под управлением устройства управления служит для выполнения арифметических и логических преобразований над данными, называемыми в этом случае операндами. Разрядность операндов обычно называют размером или длиной машинного слова.

URISC — теоретическая архитектура процессора, набор команд в которой поддерживает только одну-единственную инструкцию, и при этом обеспечивается полноту по Тьюрингу, «предельный случай» RISC.

MISC — вид процессорной архитектуры, предполагающий использование максимально простой системы команд с укладкой нескольких команд в одно большое слово и стековую организацию.

Архитекту́ра компью́тера — концептуальная модель компьютерной системы, воплощённая в её компонентах, их взаимодействии между собой и с окружением, включающая также принципы её проектирования и развития. Аспекты реализации не являются частью архитектуры.

К1801ВМ1 — однокристальный 16-разрядный микропроцессор (ОМП).

«Электроника-60» — серия мини и микро-ЭВМ, производившихся в СССР.

Суперскалярный процессор — процессор, поддерживающий так называемый параллелизм на уровне инструкций за счёт включения в состав его вычислительного ядра нескольких одинаковых функциональных узлов. Планирование исполнения потока инструкций осуществляется динамически вычислительным ядром.

Компью́терная ши́на в архитектуре компьютера — соединение, служащее для передачи данных между функциональными блоками компьютера. В устройстве шины можно различить механический, электрический (физический) и логический (управляющий) уровни.

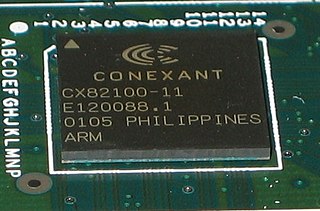

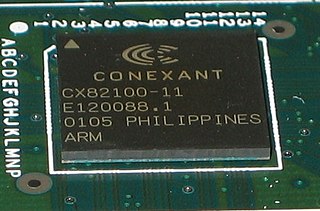

Архитектура ARM — система команд и семейство описаний и готовых топологий 32-битных и 64-битных микропроцессорных/микроконтроллерных ядер, разрабатываемых компанией ARM Limited.

Конве́йер — способ организации вычислений, используемый в современных процессорах и контроллерах с целью повышения их производительности.

Однокристальные микроконтроллеры — функционально законченный МПК, реализованный в виде одной СБИС (сверх-БИС). ОМК включает процессор, ОЗУ, ПЗУ, порты ввода-вывода для подключения внешних устройств, модули ввода аналогового сигнала АЦП, таймеры, контроллеры прерывания, контроллеры различных интерфейсов и т. д. Простейший ОМК представляет собой БИС площадью не более 1 кв. см и всего с восемью выводами.

Микроархитектура — способ, которым данная архитектура набора команд реализована в процессоре.

EPIC — микропроцессорная архитектура с явным параллелизмом команд. Термин введён в 1997 году альянсом HP и Intel для разрабатываемой архитектуры Intel Itanium. EPIC позволяет микропроцессору выполнять инструкции параллельно, опираясь на работу компилятора, а не выявляя возможность параллельной работы инструкций при помощи специальных схем. В теории, это могло упростить масштабирование вычислительной мощности процессора без увеличения тактовой частоты.

ZISC — архитектура процессора, основанная на таких технологиях, как сопоставление с образцом. Архитектура характеризуется отсутствием микрокоманд в привычном для микропроцессоров понимании. Также акроним ZISC намекает на разработанную ранее технологию RISC.

Barrel процессор, барабанный процессор, представляет собой процессор, который после каждого такта переключается между потоками команд. Эта архитектура процессора также известна как «interleaved» (чередующаяся) или «fine-grained» (мелкозернистая) временная многопоточность. В отличие от одновременной многопоточности в современных суперскалярных архитектурах, данная технология не позволяет выполнять несколько команд за один цикл.

CDC 160 – серия мини-компьютеров, выпускавшихся Control Data Corporation. Модели CDC 160 и CDC 160-A представляли собой 12-битные мини-компьютеры, выпускавшиеся с 1960 по 1965 годы. Модель CDC 160G являлась 13-битным мини-компьютером с расширенной, по сравнению с CDC 160-A, версией набора команд и режимом совместимости, в котором 13-й бит не использовался. Серия 160 была разработана Сеймуром Крэем - по слухам, в течение длинных трёхдневных выходных. Компьютер умещался в письменный стол, за которым работал оператор.