rdtsc — ассемблерная инструкция для платформ x86 и x86_64, читающая счётчик TSC и возвращающая в регистрах EDX:EAX 64-битное количество тактов с момента последнего сброса процессора.

Центра́льный проце́ссор — электронный блок либо интегральная схема, исполняющая машинные инструкции, главная часть аппаратного обеспечения компьютера или программируемого логического контроллера. Иногда этот компонент называют просто процессором.

RISC — архитектурный подход к проектированию процессоров, в которой быстродействие увеличивается за счёт такого кодирования инструкций, чтобы их декодирование было более простым, а время выполнения — меньшим. В системах команд первых RISC-процессоров даже отсутствовали команды умножения и деления. Это также облегчает повышение тактовой частоты и делает более эффективной суперскалярность.

Математический сопроцессор — сопроцессор для расширения командного множества центрального процессора и обеспечивающий его функциональностью модуля операций с плавающей запятой, для процессоров, не имеющих интегрированного модуля.

URISC — теоретическая архитектура процессора, набор команд в которой поддерживает только одну-единственную инструкцию, и при этом обеспечивается полноту по Тьюрингу, «предельный случай» RISC.

MISC — вид процессорной архитектуры, предполагающий использование максимально простой системы команд с укладкой нескольких команд в одно большое слово и стековую организацию.

Архитекту́ра компью́тера — концептуальная модель компьютерной системы, воплощённая в её компонентах, их взаимодействии между собой и с окружением, включающая также принципы её проектирования и развития. Аспекты реализации не являются частью архитектуры.

SISD или ОКОД — архитектура компьютера, в которой один процессор выполняет один поток команд, оперируя одним потоком данных. Относится к фон-Неймановской архитектуре. Один из классов вычислительных систем в классификации Флинна.

Суперскалярный процессор — процессор, поддерживающий так называемый параллелизм на уровне инструкций за счёт включения в состав его вычислительного ядра нескольких одинаковых функциональных узлов. Планирование исполнения потока инструкций осуществляется динамически вычислительным ядром.

P6 — суперскалярная суперконвейерная архитектура, разработанная компанией Intel и лежащая в основе микропроцессоров Pentium Pro, Pentium II, Pentium III, Celeron и Xeon. В отличие от x86-совместимых процессоров предыдущих поколений с CISC-ядром, процессоры архитектуры P6 имеют RISC-ядро, исполняющее сложные инструкции x86 не напрямую, а предварительно декодируя их в простые внутренние микрооперации.

NetBurst — суперскалярная гиперконвейерная микроархитектура, разработанная компанией Intel и лежавшая в основе микропроцессоров Pentium 4, Pentium D, Celeron и Xeon в 2000-2007 годах.

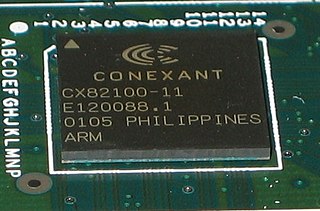

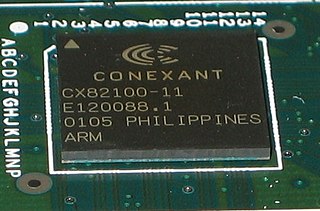

Архитектура ARM — система команд и семейство описаний и готовых топологий 32-битных и 64-битных микропроцессорных/микроконтроллерных ядер, разрабатываемых компанией ARM Limited.

Конве́йер — способ организации вычислений, используемый в современных процессорах и контроллерах с целью повышения их производительности.

EPIC — микропроцессорная архитектура с явным параллелизмом команд. Термин введён в 1997 году альянсом HP и Intel для разрабатываемой архитектуры Intel Itanium. EPIC позволяет микропроцессору выполнять инструкции параллельно, опираясь на работу компилятора, а не выявляя возможность параллельной работы инструкций при помощи специальных схем. В теории, это могло упростить масштабирование вычислительной мощности процессора без увеличения тактовой частоты.

Таксономия (Классификация) Флинна — общая классификация архитектур ЭВМ по признакам наличия параллелизма в потоках команд и данных. Была предложена Майклом Флинном в 1966 году и расширена в 1972 году.

Управля́ющий автома́т, устро́йство управле́ния проце́ссором (УУ) — блок, устройство, компонент аппаратного обеспечения компьютеров. Представляет собой конечный дискретный автомат. Структурно устройство управления состоит из: дешифратора команд (операций), регистра команд, узла формирования (вычисления) текущего исполнительного адреса, счётчика команд.

Параллелизм на уровне команд является мерой того, какое множество операций в компьютерной программе может выполняться одновременно. Потенциальное совмещение выполнения команд называется «параллелизмом на уровне команд».

Barrel процессор, барабанный процессор, представляет собой процессор, который после каждого такта переключается между потоками команд. Эта архитектура процессора также известна как «interleaved» (чередующаяся) или «fine-grained» (мелкозернистая) временная многопоточность. В отличие от одновременной многопоточности в современных суперскалярных архитектурах, данная технология не позволяет выполнять несколько команд за один цикл.

Halt and Catch Fire — гипотетическая ассемблерная команда, при выполнении которой центральный процессор компьютера перестает выполнять дальнейшие команды, из-за чего для восстановления работоспособности необходимо выполнить «жесткую» перезагрузку.