POSIX — набор стандартов, описывающих интерфейсы между операционной системой и прикладной программой, библиотеку языка C и набор приложений и их интерфейсов. Стандарт создан для обеспечения совместимости различных UNIX-подобных операционных систем и переносимости прикладных программ на уровне исходного кода, но может быть использован и для не-Unix систем.

Unix — семейство переносимых, многозадачных и многопользовательских операционных систем, которые основаны на идеях оригинального проекта AT&T Unix, разработанного в 1970-х годах в исследовательском центре Bell Labs Кеном Томпсоном, Деннисом Ритчи и другими.

Сетевая модель OSI — сетевая модель стека (магазина) сетевых протоколов OSI/ISO. Посредством данной модели различные сетевые устройства могут взаимодействовать друг с другом. Модель определяет различные уровни взаимодействия систем. Каждый уровень выполняет определённые функции при таком взаимодействии.

VHDL — язык описания аппаратуры интегральных схем. Язык проектирования VHDL является базовым языком при разработке аппаратуры современных вычислительных систем.

SPARC — архитектура RISC-микропроцессоров, первоначально разработанная в 1985 году компанией Sun Microsystems.

Verilog, Verilog HDL — это язык описания аппаратуры, используемый для описания и моделирования электронных систем. Verilog HDL, не следует путать с VHDL, наиболее часто используется в проектировании, верификации и реализации аналоговых, цифровых и смешанных электронных систем на различных уровнях абстракции.

RTEMS — свободная операционная система реального времени с открытым исходным кодом, разработанная для встраиваемых систем.

OpenRISC — открытый микропроцессор архитектуры RISC с открытым исходным кодом на языке описания аппаратного обеспечения Verilog. Проект создан сообществом OpenCores и распространяется по лицензии GNU LGPL. OpenRISC воплощён аппаратно и успешно производится в виде интегральных микросхем и ПЛИС.

Систе́ма на криста́лле — электронная схема, выполняющая функции целого устройства и размещённая на одной интегральной схеме.

SystemC — язык проектирования и верификации моделей системного уровня, реализованный в виде C++ библиотеки с открытым исходным кодом. Библиотека включает в себя ядро событийного моделирования, что позволяет получить исполняемую модель устройства. Язык применяется для построения транзакционных и поведенческих моделей, а также для высокоуровневого синтеза.

Aldec, Inc. — частная компания, которая производит программное и аппаратное обеспечение для автоматизации проектирования микроэлектроники. Штаб-квартира фирмы расположена в Хендерсоне (Невада), США, также имеются офисы в Канаде, Японии, Польше и Украине.

IEEE-488 — спецификация международного стандарта, описывающая интерфейс подключения к шине цифровых измерительных приборов.

Проектирование на основе стандартных ячеек — метод проектирования интегральных схем с преобладанием цифровых элементов. В данном методе наиболее низкий уровень проектирования СБИС скрыт от проектировщика абстрактными логическими элементами. Методология проектирования на базе ячеек позволяет одним разработчикам сфокусироваться на высокоуровневом аспекте цифрового дизайна, пока другие разработчики заняты физическими реализациями ячеек. Вместе с достижениями полупроводникового производства методология стандартных ячеек отвечает за возможность проектирования как простых интегральных схем, число которых составляет несколько тысяч транзисторов, так и сложнейших: СБИС и систем на кристалле (СнК) с числом транзисторов, достигающим десятков миллиардов.

Active-HDL — среда разработки, моделирования и верификации проектов для программируемых логических интегральных схем, разработанная фирмой Aldec. Первая версия программы вышла в 1997 году.

Cádence Design Systems, Inc — компания, занимающаяся разработкой программного обеспечения для автоматизации проектирования электронных устройств и предоставлением инженерных услуг. Основана в 1988 году в результате объединения компаний SDA Systems и ECAD. В течение многих лет была крупнейшей компанией в EDA индустрии.

SystemVerilog — язык описания и верификации аппаратуры, являющийся расширением языка Verilog.

Логический синтез в электронике — процесс получения списка соединений логических вентилей из абстрактной модели поведения логической схемы. Наиболее распространенный пример этого процесса — синтез спецификаций, написанных на языках описания аппаратуры. Синтез выполняют программы-синтезаторы, способные оптимизировать проект согласно различным особенностям устройства, таким как временные ограничения, площадь и используемые компоненты. Такие программы обычно специализируются на генерации битовых потоков для программируемой логики или создании интегральных схем специального назначения. Логический синтез является составной частью автоматизации проектирования электронных приборов.

Язык описания аппаратуры — специализированный компьютерный язык, используемый для описания структуры и поведения электронных схем, чаще всего цифровых логических схем.

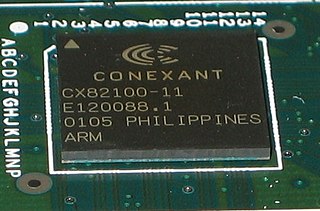

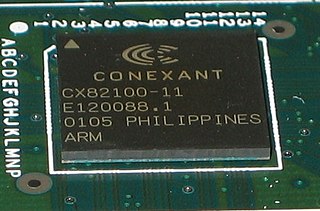

Прогрессивная Архитектура Шины Микроконтроллера (AMBA) [фирмы] ARM - это открытый стандарт требований внутрикристалльных межсоединений для соединения и управления функциональными блоками в разработках system-on-a-chip (SoC). Она облегчает развитие многопроцессорных разработок с большим числом контроллеров и периферии. Несмотря на название, с самого своего начала, AMBA имела виды, уходящие далеко за границы микроконтроллерных устройств. Сегодня AMBA широко применяется в ряде частей ASIC и SoC, включая прикладные процессоры, применяемые в современных небольших переносных устройствах вроде smartphones. AMBA - это зарегистрированная торговая марка ARM Ltd.

IEEE 1355—1995 — коммуникационный стандарт последовательного интерфейса, предназначенный для передачи данных в гетерогенных вычислительных сетях.