Cadence Design Systems

| Cadence Design Systems | |

|---|---|

| | |

| |

| Тип | Публичная компания |

| Листинг на бирже | NASDAQ: CDNS[3] |

| Основание | 1988[4] |

| Расположение | |

| Ключевые фигуры | Лип-Бу Тан[англ.] (CEO) |

| Отрасль | Программное обеспечение |

| Оборот | ▲4,09 млрд $ (2023 год)[1] |

| Операционная прибыль | ▲1,23 млрд $ (2023) |

| Чистая прибыль | 1,04 млрд $ (2023) |

| Активы | 5,67 млрд $ (2023) |

| Капитализация | 3,4 млрд $ (2023) |

| Число сотрудников | 4400 (2010) [2] |

| Сайт | cadence.com (англ.) |

Cádence Design Systems, Inc (NASDAQ: CDNS) — компания, занимающаяся разработкой программного обеспечения для автоматизации проектирования электронных устройств (англ. EDA) и предоставлением инженерных услуг. Основана в 1988 году в результате объединения компаний SDA Systems и ECAD. В течение многих лет была крупнейшей компанией в EDA индустрии.

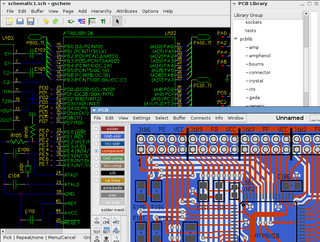

Штаб-квартира Cadence находится в Сан-Хосе, Калифорния. Компания является одним из крупнейших поставщиков технологий проектирования электронных устройств и инженерных услуг в EDA индустрии. Основным продуктом компании является программное обеспечение для проектирования микросхем[6] и печатных плат[7].

В Cadence работает примерно 5000 сотрудников и на 2008 год доходы компании составили 1,04 млрд $. В ноябре 2007 года Cadence была включена журналом San Jose Magazine в список 50 лучших работодателей в Кремниевой долине.

В январе 2009 года было объявлено о назначении Лип-Бу Тана[англ.] президентом и CEO компании. Тан до этого занимал должность CEO в компании Walden International. Он входил в совет директоров Cadence с 2004 года.

Основные продукты

Продукты Cadence нацелены на различные типы проектирования и верификации:

- Virtuoso Platform — инструменты для проектирования интегральных схем[8]; в него входит структурное представление, поведенческое моделирование (Verilog-AMS), симуляция схемы, полный макет, физическая верификация. Используется, в основном, для проектирования аналоговых схем, но так же используется для проектирования памяти и FPGA.

- Genus Platform — инструменты для проектирования, тестирования и синтеза цифровых интегральных схем[9].

- Xcelium Platform — инструменты для симуляции, функциональной верификации RTL, включая модели, основанные на Verilog, VHDL и SystemC. Сюда входит формальная верификация, проверка формальной эквиваленции и эмуляция[10].

- Verification IP[11]

- Allegro Platform — инструменты для совместного проектирования интегральных схем и печатных плат[10].

- OrCAD/PSpice — Инструменты для небольших компаний проектирования и индивидуальных разработчиков[10].

Примечания

- ↑ FORM 10-K. SEK. Дата обращения: 28 июля 2024.

- ↑ Cadence Company Overview (англ.). Архивировано 16 мая 2008 года.

- ↑ Cadence Design Systems Inc. // Polygon.io

- ↑ ROR Data — v1.19 — 2023. — doi:10.5281/ZENODO.7644942

- ↑ https://www.cadence.com/en_US/home/company/contact-us.html

- ↑ Design on Diagonal Path in Pursuit of a Faster Chip Архивная копия от 26 октября 2017 на Wayback Machine, John Markoff, New York Times, February 26, 2007

- ↑ Cadence Acquires Software Company, New York Times, April 11, 1990. Article describes Cadence acquiring a printed circuit design software company

- ↑ Course description from University of Colorado Архивировано 24 июня 2007 года.

- ↑ Tutorial from MIT course. Дата обращения: 24 июня 2010. Архивировано 27 мая 2008 года.

- ↑ 1 2 3 UNIX Software and CAD tools. Carleton University. Архивировано из оригинала 30 апреля 2012 года.

- ↑ Verification IP (англ.). Архивировано 22 мая 2010 года.