Центра́льный проце́ссор — электронный блок либо интегральная схема, исполняющая машинные инструкции, главная часть аппаратного обеспечения компьютера или программируемого логического контроллера. Иногда этот компонент называют просто процессором.

RISC — архитектурный подход к проектированию процессоров, в которой быстродействие увеличивается за счёт такого кодирования инструкций, чтобы их декодирование было более простым, а время выполнения — меньшим. В системах команд первых RISC-процессоров даже отсутствовали команды умножения и деления. Это также облегчает повышение тактовой частоты и делает более эффективной суперскалярность.

CISC — тип процессорной архитектуры, которая характеризуется следующим набором свойств:

- нефиксированное значение длины команды;

- арифметические действия кодируются в одной команде;

- небольшое число регистров, каждый из которых выполняет строго определённую функцию.

MIPS — система команд и микропроцессорных архитектур, разработанных компанией MIPS Computer Systems в соответствии с концепцией проектирования процессоров RISC. Ранние модели процессора имели 32-битное машинное слово, позднее появились его 64-битные версии. Существует множество модификаций процессора, включая MIPS I, MIPS II, MIPS III, MIPS IV, MIPS V, MIPS32 и MIPS64, из них действующими являются MIPS32 и MIPS64. MIPS32 и MIPS64 определяют как набор регистров управления, так и набор команд.

VLIW — архитектура процессоров с несколькими вычислительными устройствами. Характеризуется тем, что одна инструкция процессора содержит несколько операций, которые должны выполняться параллельно. Фактически это «видимое программисту» микропрограммное управление, когда машинный код представляет собой лишь немного свёрнутый микрокод для непосредственного управления аппаратурой.

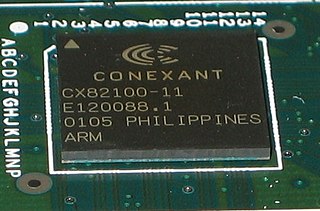

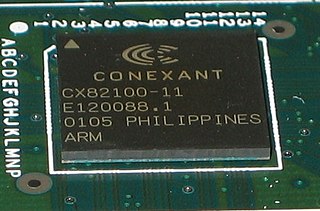

Архитектура ARM — система команд и семейство описаний и готовых топологий 32-битных и 64-битных микропроцессорных/микроконтроллерных ядер, разрабатываемых компанией ARM Limited.

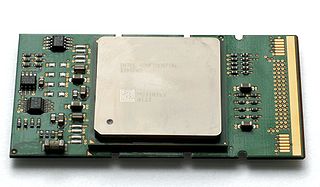

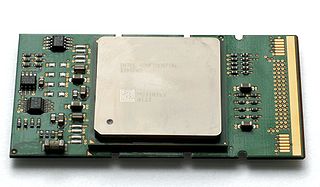

i960 — RISC-процессор Intel, популярный в 1990-х годах. Применялся во встраиваемых системах и микроконтроллерах.

AVR32 — 32-битные микроконтроллеры архитектуры RISC, анонсированные фирмой Atmel в 2006 году. Призваны конкурировать с архитектурами фирмы ARM. Могут использоваться в КПК и других мобильных высокопроизводительных устройствах. Обладают примечательным соотношением производительность/тактовая частота. Имеют 2 семейства: AVR32 AP и AVR32 UC3.

Конве́йер — способ организации вычислений, используемый в современных процессорах и контроллерах с целью повышения их производительности.

MMIX — 64-битная RISC архитектура компьютера, разработанная Дональдом Кнутом с существенным вкладом Джона Хеннесси и Ричарда Сайтса. По словам самого Дональда Кнута:

MMIX — компьютер, цель которого проиллюстрировать аспекты программирования на машинном уровне. В моих книгах Искусство программирования он заменяет MIX, машину стиля 1960-х годов, которая играла ту же роль. Я старался так проектировать MMIX, чтобы его машинный язык был простым, изящным, удобным для изучения. В то же время я старался включить все сложности, которые необходимы для достижения высокой эффективности на практике, так что MMIX может быть реально построен и даже может быть конкурентоспособным с некоторыми из самых быстрых компьютеров общего назначения на рынке.

Ниже приведен список систем команд

128 бит — в информатике и компьютерной технике используется для обозначения структур и типов данных, размер которых в памяти компьютеров занимает 128 бит, что равно 16 байтам. Архитектуры компьютеров, которые базируются на регистрах, адресных шинах или шинах данных, размеры которых составляют 128 бит, называются 128-битными архитектурами.

Микроархитектура — способ, которым данная архитектура набора команд реализована в процессоре.

EPIC — микропроцессорная архитектура с явным параллелизмом команд. Термин введён в 1997 году альянсом HP и Intel для разрабатываемой архитектуры Intel Itanium. EPIC позволяет микропроцессору выполнять инструкции параллельно, опираясь на работу компилятора, а не выявляя возможность параллельной работы инструкций при помощи специальных схем. В теории, это могло упростить масштабирование вычислительной мощности процессора без увеличения тактовой частоты.

64 бита в информатике и вычислительной технике используется для обозначения структур и типов данных, размер которых в памяти компьютеров составляет 64 бита, что равно 8 8-битовым байтам. Архитектуры компьютеров, которые широко используют регистры, адресные шины или шины данных, разрядности 64 бита, называются 64-битными архитектурами.

В компьютерной архитектуре — 32-разрядные целые, адреса памяти или другие типы данных размером 32 бита. 32-битные ЦПУ и АЛУ — архитектуры, основанные на регистрах и шинах данного размера.

Параллелизм на уровне команд является мерой того, какое множество операций в компьютерной программе может выполняться одновременно. Потенциальное совмещение выполнения команд называется «параллелизмом на уровне команд».

RISC-V — расширяемая открытая и свободная система команд и процессорная архитектура на основе концепции RISC, предназначенная для создания процессоров/микроконтроллеров и разработки ПО. Спецификации архитектурных описаний RISC-V свободно доступны и бесплатны для любого использования, включая коммерческие реализации непосредственно в кремнии или для конфигурирования ПЛИС. Участие в проектировании и обсуждении спецификаций архитектурных описаний открытое. Система команд имеет зарезервированные в спецификации биты для кодирования расширений без ограничения области применения.

CompactRISC — семейство архитектур наборов команд от National Semiconductor. Архитектура была разработана в соответствии с принципом сокращённого набора команд и в основном используется в микроконтроллерах. Примерами архитектур этого семейства являются 16-битные CR16 и CR16C и 32-битная CRX.

R10000 — RISC-микропроцессор, реализующий набор инструкций MIPS IV. Разработан компанией MIPS Technoligies, Inc.. Главные разработчики — Крис Роуэн и Кеннет С. Йегер. R10000 построен на основе микроархитектуры ANDES. R10000 во многом заменил R8000 в высокопроизводительном сегменте и R4400 в других применениях. MTI является фаблесс-компанией, процессоры R10000 изготавливались NEC и Toshiba. Предыдущие производители микропроцессоров MIPS, IDT и другие не производили R10000, так как это было более дорогим, чем R4000 и R4400.