rdtsc — ассемблерная инструкция для платформ x86 и x86_64, читающая счётчик TSC и возвращающая в регистрах EDX:EAX 64-битное количество тактов с момента последнего сброса процессора.

Форт — один из первых конкатенативных языков программирования, в котором программы записываются последовательностью лексем. Математические выражения представляются постфиксной записью при использовании стековой нотации. Поддерживает механизмы метарасширения семантики и синтаксиса языка для адаптации к нужной предметной области. Синтаксис базового уровня в Форте прост и состоит из единственного правила: «все определения разделяются пробелами». Определения Форта могут иметь любое сочетание символов.

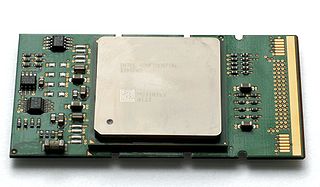

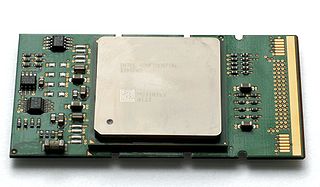

x86 — архитектура процессора и одноимённый набор команд, впервые реализованные в процессорах компании Intel.

Центра́льный проце́ссор — электронный блок либо интегральная схема, исполняющая машинные инструкции, главная часть аппаратного обеспечения компьютера или программируемого логического контроллера. Иногда этот компонент называют просто процессором.

RISC — архитектурный подход к проектированию процессоров, в которой быстродействие увеличивается за счёт такого кодирования инструкций, чтобы их декодирование было более простым, а время выполнения — меньшим. В системах команд первых RISC-процессоров даже отсутствовали команды умножения и деления. Это также облегчает повышение тактовой частоты и делает более эффективной суперскалярность.

Систе́ма кома́нд — соглашение о предоставляемых архитектурой средствах программирования, а именно:

- определённых типах данных,

- инструкций,

- системы регистров,

- методов адресации,

- моделей памяти,

- способов обработки прерываний и исключений,

- методов ввода и вывода.

CISC — тип процессорной архитектуры, которая характеризуется следующим набором свойств:

- нефиксированное значение длины команды;

- арифметические действия кодируются в одной команде;

- небольшое число регистров, каждый из которых выполняет строго определённую функцию.

Цифровой сигнальный процессор (англ. digital signal processor, DSP, цифровой процессор обработки сигналов — специализированный микропроцессор, предназначенный для обработки оцифрованных сигналов.

VLIW — архитектура процессоров с несколькими вычислительными устройствами. Характеризуется тем, что одна инструкция процессора содержит несколько операций, которые должны выполняться параллельно. Фактически это «видимое программисту» микропрограммное управление, когда машинный код представляет собой лишь немного свёрнутый микрокод для непосредственного управления аппаратурой.

Математический сопроцессор — сопроцессор для расширения командного множества центрального процессора и обеспечивающий его функциональностью модуля операций с плавающей запятой, для процессоров, не имеющих интегрированного модуля.

URISC — теоретическая архитектура процессора, набор команд в которой поддерживает только одну-единственную инструкцию, и при этом обеспечивается полноту по Тьюрингу, «предельный случай» RISC.

Архитекту́ра компью́тера — концептуальная модель компьютерной системы, воплощённая в её компонентах, их взаимодействии между собой и с окружением, включающая также принципы её проектирования и развития. Аспекты реализации не являются частью архитектуры.

Однокристальные микроконтроллеры — функционально законченный МПК, реализованный в виде одной СБИС (сверх-БИС). ОМК включает процессор, ОЗУ, ПЗУ, порты ввода-вывода для подключения внешних устройств, модули ввода аналогового сигнала АЦП, таймеры, контроллеры прерывания, контроллеры различных интерфейсов и т. д. Простейший ОМК представляет собой БИС площадью не более 1 кв. см и всего с восемью выводами.

Микроархитектура — способ, которым данная архитектура набора команд реализована в процессоре.

EPIC — микропроцессорная архитектура с явным параллелизмом команд. Термин введён в 1997 году альянсом HP и Intel для разрабатываемой архитектуры Intel Itanium. EPIC позволяет микропроцессору выполнять инструкции параллельно, опираясь на работу компилятора, а не выявляя возможность параллельной работы инструкций при помощи специальных схем. В теории, это могло упростить масштабирование вычислительной мощности процессора без увеличения тактовой частоты.

Таксономия (Классификация) Флинна — общая классификация архитектур ЭВМ по признакам наличия параллелизма в потоках команд и данных. Была предложена Майклом Флинном в 1966 году и расширена в 1972 году.

ZISC — архитектура процессора, основанная на таких технологиях, как сопоставление с образцом. Архитектура характеризуется отсутствием микрокоманд в привычном для микропроцессоров понимании. Также акроним ZISC намекает на разработанную ранее технологию RISC.

Transport triggered architecture (TTA) — вариант архитектуры микропроцессоров, в которой программы непосредственно управляют внутренними соединениями (шинами) между блоками процессора. Вычисления являются побочным эффектом передачи данных между блоками: запись данных на входной порт функционального устройства приводит к началу их обработки данным устройством. Благодаря модульной структуре, TTA-архитектура подходит для проектирования проблемно-ориентированных процессоров (ASIP), при этом TTA-процессоры получаются универсальнее и дешевле чем аппаратные ускорители для фиксированных функций.

Процессор в памяти — процессор, тесно интегрированный в основную память, выполненный, как правило, на одном кремниевом кристалле.