RISC — архитектурный подход к проектированию процессоров, в которой быстродействие увеличивается за счёт такого кодирования инструкций, чтобы их декодирование было более простым, а время выполнения — меньшим. В системах команд первых RISC-процессоров даже отсутствовали команды умножения и деления. Это также облегчает повышение тактовой частоты и делает более эффективной суперскалярность.

CISC — тип процессорной архитектуры, которая характеризуется следующим набором свойств:

- нефиксированное значение длины команды;

- арифметические действия кодируются в одной команде;

- небольшое число регистров, каждый из которых выполняет строго определённую функцию.

SPARC — архитектура RISC-микропроцессоров, первоначально разработанная в 1985 году компанией Sun Microsystems.

Архитекту́ра компью́тера — концептуальная модель компьютерной системы, воплощённая в её компонентах, их взаимодействии между собой и с окружением, включающая также принципы её проектирования и развития. Аспекты реализации не являются частью архитектуры.

SuperH — название микропроцессорной и микроконтроллерной архитектуры, являющееся торговой маркой. В основе SuperH лежит 32-разрядная RISC-архитектура, используемая в большом количестве встраиваемых систем.

P6 — суперскалярная суперконвейерная архитектура, разработанная компанией Intel и лежащая в основе микропроцессоров Pentium Pro, Pentium II, Pentium III, Celeron и Xeon. В отличие от x86-совместимых процессоров предыдущих поколений с CISC-ядром, процессоры архитектуры P6 имеют RISC-ядро, исполняющее сложные инструкции x86 не напрямую, а предварительно декодируя их в простые внутренние микрооперации.

Регистр флагов или слово состояния процессора (ССП) — специализированный регистр, отражающий текущее состояние процессора.

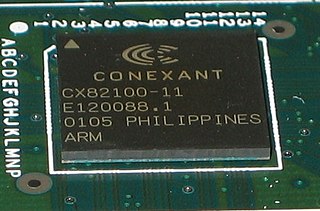

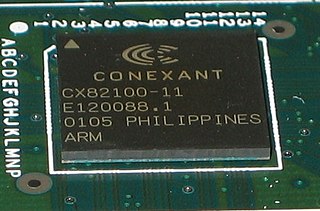

Архитектура ARM — система команд и семейство описаний и готовых топологий 32-битных и 64-битных микропроцессорных/микроконтроллерных ядер, разрабатываемых компанией ARM Limited.

Конве́йер — способ организации вычислений, используемый в современных процессорах и контроллерах с целью повышения их производительности.

Extended MMX, также известное как EMMI — это расширение набора инструкций MMX, предложенное компанией Cyrix и внедрившей его в свои процессоры 6x86MX и MII. EMMI расширяет набор инструкций MMX 12-ю новыми командами, полезными при мультимедийной обработке. Это расширение не задействовано по умолчанию, и перед использованием требует включения с помощью BIOS или программно. EMMI никогда не пользовалось большой поддержкой со стороны производителей ПО или признанием конкурентов Cyrix. Это расширение больше не включалось в набор инструкций процессоров, планирующихся к выходу после MII.

Ниже приведен список систем команд

EPIC — микропроцессорная архитектура с явным параллелизмом команд. Термин введён в 1997 году альянсом HP и Intel для разрабатываемой архитектуры Intel Itanium. EPIC позволяет микропроцессору выполнять инструкции параллельно, опираясь на работу компилятора, а не выявляя возможность параллельной работы инструкций при помощи специальных схем. В теории, это могло упростить масштабирование вычислительной мощности процессора без увеличения тактовой частоты.

Кэш микропроце́ссора — кэш, используемый микропроцессором компьютера для уменьшения среднего времени доступа к компьютерной памяти. Является одним из верхних уровней иерархии памяти. Кэш использует небольшую, очень быструю память, которая хранит копии часто используемых данных из основной памяти. Если большая часть запросов в память будет обрабатываться кэшем, средняя задержка обращения к памяти будет приближаться к задержкам работы кэша.

MC88100 — микропроцессор, разработанный компанией Motorola. Анонсирован в 1988 году и является первой реализацией системы команд 88000. Ему на смену в начале 1990-х пришёл MC88110. Вместе с микросхемой Motorola MC88200 применялся в качестве базового элемента в линейке военных продуктов Thomson-CSF, рассчитанных на процессоры, реализующие RISC-архитектуру

64 бита в информатике и вычислительной технике используется для обозначения структур и типов данных, размер которых в памяти компьютеров составляет 64 бита, что равно 8 8-битовым байтам. Архитектуры компьютеров, которые широко используют регистры, адресные шины или шины данных, разрядности 64 бита, называются 64-битными архитектурами.

ZISC — архитектура процессора, основанная на таких технологиях, как сопоставление с образцом. Архитектура характеризуется отсутствием микрокоманд в привычном для микропроцессоров понимании. Также акроним ZISC намекает на разработанную ранее технологию RISC.

DLX — учебная 32-битная конвейерная микропроцессорная RISC-архитектура, разработанная Джоном Хеннесси и Дэвидом Паттерсоном. DLX является упрощенным MIPS и имеет архитектуру load/store. Предназначен, в основном, для обучения и широко используется в университетских курсах по архитектуре компьютеров.

Transport triggered architecture (TTA) — вариант архитектуры микропроцессоров, в которой программы непосредственно управляют внутренними соединениями (шинами) между блоками процессора. Вычисления являются побочным эффектом передачи данных между блоками: запись данных на входной порт функционального устройства приводит к началу их обработки данным устройством. Благодаря модульной структуре, TTA-архитектура подходит для проектирования проблемно-ориентированных процессоров (ASIP), при этом TTA-процессоры получаются универсальнее и дешевле чем аппаратные ускорители для фиксированных функций.

RISC-V — расширяемая открытая и свободная система команд и процессорная архитектура на основе концепции RISC, предназначенная для создания процессоров/микроконтроллеров и разработки ПО. Спецификации архитектурных описаний RISC-V свободно доступны и бесплатны для любого использования, включая коммерческие реализации непосредственно в кремнии или для конфигурирования ПЛИС. Участие в проектировании и обсуждении спецификаций архитектурных описаний открытое. Система команд имеет зарезервированные в спецификации биты для кодирования расширений без ограничения области применения.

В компьютерной архитектуре 256-битными числами, адресами памяти и другими объектами данных называются те, которые имеют размер в 256 бит. Также 256-битными являются те ЦПУ и АЛУ, которые построены на регистрах, шинах адреса и шинах данных такого размера.