RISC — архитектурный подход к проектированию процессоров, в которой быстродействие увеличивается за счёт такого кодирования инструкций, чтобы их декодирование было более простым, а время выполнения — меньшим. В системах команд первых RISC-процессоров даже отсутствовали команды умножения и деления. Это также облегчает повышение тактовой частоты и делает более эффективной суперскалярность.

SSE — это SIMD- набор инструкций, разработанный Intel и впервые представленный в процессорах серии Pentium III как ответ на аналогичный набор инструкций 3DNow! от AMD, который был представлен годом раньше. Первоначально названием этих инструкций было KNI — Katmai New Instructions.

CISC — тип процессорной архитектуры, которая характеризуется следующим набором свойств:

- нефиксированное значение длины команды;

- арифметические действия кодируются в одной команде;

- небольшое число регистров, каждый из которых выполняет строго определённую функцию.

VLIW — архитектура процессоров с несколькими вычислительными устройствами. Характеризуется тем, что одна инструкция процессора содержит несколько операций, которые должны выполняться параллельно. Фактически это «видимое программисту» микропрограммное управление, когда машинный код представляет собой лишь немного свёрнутый микрокод для непосредственного управления аппаратурой.

SIMD — принцип компьютерных вычислений, позволяющий обеспечить параллелизм на уровне данных. Один из классов вычислительных систем в классификации Флинна.

SISD или ОКОД — архитектура компьютера, в которой один процессор выполняет один поток команд, оперируя одним потоком данных. Относится к фон-Неймановской архитектуре. Один из классов вычислительных систем в классификации Флинна.

Суперскалярный процессор — процессор, поддерживающий так называемый параллелизм на уровне инструкций за счёт включения в состав его вычислительного ядра нескольких одинаковых функциональных узлов. Планирование исполнения потока инструкций осуществляется динамически вычислительным ядром.

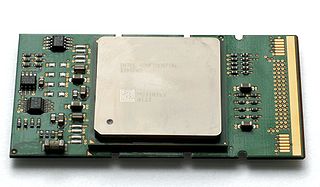

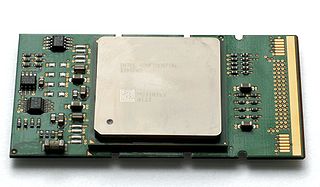

P6 — суперскалярная суперконвейерная архитектура, разработанная компанией Intel и лежащая в основе микропроцессоров Pentium Pro, Pentium II, Pentium III, Celeron и Xeon. В отличие от x86-совместимых процессоров предыдущих поколений с CISC-ядром, процессоры архитектуры P6 имеют RISC-ядро, исполняющее сложные инструкции x86 не напрямую, а предварительно декодируя их в простые внутренние микрооперации.

NetBurst — суперскалярная гиперконвейерная микроархитектура, разработанная компанией Intel и лежавшая в основе микропроцессоров Pentium 4, Pentium D, Celeron и Xeon в 2000-2007 годах.

Конве́йер — способ организации вычислений, используемый в современных процессорах и контроллерах с целью повышения их производительности.

Внеочередное исполнение машинных инструкций — исполнение машинных инструкций не в порядке следования в машинном коде, а в порядке готовности к выполнению. Реализуется с целью повышения производительности вычислительных устройств.

Микроархитектура — способ, которым данная архитектура набора команд реализована в процессоре.

EPIC — микропроцессорная архитектура с явным параллелизмом команд. Термин введён в 1997 году альянсом HP и Intel для разрабатываемой архитектуры Intel Itanium. EPIC позволяет микропроцессору выполнять инструкции параллельно, опираясь на работу компилятора, а не выявляя возможность параллельной работы инструкций при помощи специальных схем. В теории, это могло упростить масштабирование вычислительной мощности процессора без увеличения тактовой частоты.

Кэш микропроце́ссора — кэш, используемый микропроцессором компьютера для уменьшения среднего времени доступа к компьютерной памяти. Является одним из верхних уровней иерархии памяти. Кэш использует небольшую, очень быструю память, которая хранит копии часто используемых данных из основной памяти. Если большая часть запросов в память будет обрабатываться кэшем, средняя задержка обращения к памяти будет приближаться к задержкам работы кэша.

Таксономия (Классификация) Флинна — общая классификация архитектур ЭВМ по признакам наличия параллелизма в потоках команд и данных. Была предложена Майклом Флинном в 1966 году и расширена в 1972 году.

Одновременная многопоточность — одна из двух главных форм многопоточности, которая может быть реализована в процессорах аппаратно. Второй формой является временная многопоточность. Технология одновременной многопоточности позволяет исполнять инструкции из нескольких независимых потоков выполнения на множестве функциональных модулей суперскалярного микропроцессора в одном цикле.

В компьютерной архитектуре, предвыборкой кода называют технологию, используемую в микропроцессоре для увеличения скорости исполнения программ, уменьшая время, в течение которого процессор находится в состоянии ожидания из-за отсутствия инструкций для исполнения.

Параллелизм на уровне команд является мерой того, какое множество операций в компьютерной программе может выполняться одновременно. Потенциальное совмещение выполнения команд называется «параллелизмом на уровне команд».

Barrel процессор, барабанный процессор, представляет собой процессор, который после каждого такта переключается между потоками команд. Эта архитектура процессора также известна как «interleaved» (чередующаяся) или «fine-grained» (мелкозернистая) временная многопоточность. В отличие от одновременной многопоточности в современных суперскалярных архитектурах, данная технология не позволяет выполнять несколько команд за один цикл.